1. Bevezetés

rendszerben szükség van – az egyszerű mikrovezérlő áramköröktől a nagysebességű adatátviteli rendszerekig.

Az oszcillátor kimeneti jelének kompatibilisnek kell lennie a következő logikai családdal vagy interfésszel. Az évtizedek során különböző kimeneti szabványok alakultak ki, mindegyik a maga korának és alkalmazásának igényeihez igazítva.

Ez a dokumentum átfogó áttekintést nyújt a Kvarcoszcillátorok hét leggyakoribb kimeneti jeltípusáról: CMOS, TTL, vágott szinuszjel, szinusz, LVPECL, LVDS és HCSL.

Minden típusnál bemutatjuk a történeti fejlődést, az elektromos jellemzőket, a tipikus jelalakot és az előnyben részesített alkalmazási területeket.

2. Történeti fejlődés

A kimeneti jeltípusok fejlődése szorosan összefügg a félvezető-technológia evolúciójával és az órajel-frekvenciákkal és jelintegritással szemben támasztott növekvő követelményekkel:

2.1 TTL (tranzisztor-tranzisztor logika) – kb. 1964-től

A TTL az első széles körben elterjedt digitális logikai szabványok egyike volt, amelyet a Texas Instruments vezetett be 7400-as sorozatként. A TTL kimenetű oszcillátorok 5 V tápfeszültséggel működnek, és közvetlenül TTL kapukkal kompatibilis szinteket biztosítanak. A szabvány évtizedeken át meghatározta a digitális elektronikát, és a 90-es évekig a domináns logikai szabvány volt.

2.2 CMOS (Complementary Metal-Oxide-Semiconductor) – kb. 1968-tól

A CMOS technológiát eredetileg RCA-hoz fejlesztették ki, és rendkívül alacsony nyugalmi áramfelvétel jellemzi. A CMOS oszcillátorok síntől sínig terjedő kimeneti jeleket szolgáltatnak, ami azt jelenti, hogy a kimenet szinte teljes egészében 0 V és VCC között oszcillál. A folyamatos miniatürizálásnak és az alacsonyabb tápfeszültségek (3,3 V, 2,5 V, 1,8 V) felé történő trendnek köszönhetően a CMOS az RCA oszcillátorok legszélesebb körben használt kimeneti szabványává vált.

2.3 Sinus – az oszcillátortechnika kezdeteitől

A szinuszos kimeneti jelek olyan régiek, mint maga az oszcillátor technológia. Az oszcillátorok fizikailag szinuszosan oszcillálnak; minden más jelalakot a downstream áramkörök generálnak. A szinuszos kimeneteket előnyben részesítik a nagyfrekvenciás technológiában, a mérőműszerekben és az analóg jelfeldolgozásban, mivel nem generálnak felharmonikusokat.

2.4 Clipped Sine Wave – kb. a 70-es évektől

A Clipped Sine Wave kimenet kompromisszumot képez a szinuszos és a négyszögjel-kimenet között. A szinuszjelet a csúcsokon levágják (clippelik), ami meredekebb éleket eredményez, mint a tiszta szinusz, de kevesebb felharmonikust, mint a négyszögjel. Ez a kimeneti típus különösen a távközlésben és a régebbi nagyfrekvenciás alkalmazásokban terjedt el. A Clipped Sine Wave IC-ket ma főként még TCXO-kban használják. Ezzel a technológiával lényegesen energiatakarékosabb TCXO-k építhetők, mint a CMOS technológiával. A CSW-TCXO-kat ezért referenciaként használják navigációs készülékekben, segélyhívó rendszerekben és átjárókban. Mindenhol, ahol jelhatótávolság (rádió) és nagy pontosságú pozícionálás szükséges.

2.5 LVPECL (Low-Voltage Positive Emitter-Coupled Logic) – kb. a 90-es évektől

Az egyre magasabb órajel-frekvenciák iránti igénnyel a hálózati és távközlési rendszerekben jött létre az LVPECL mint gyors differenciális kimeneti logika. Az LVPECL a klasszikus ECL technikán (Emitter-Coupled Logic) alapul, amelyet már a 60-as években fejlesztettek ki nagysebességű alkalmazásokhoz, és alacsonyabb tápfeszültséghez adaptálja (3,3 V a -5,2 V helyett). Az LVPECL extrém rövid kapcsolási időket kínál, és jóval 1 GHz feletti frekvenciákra alkalmas.

2.6 LVDS (Low-Voltage Differential Signaling) – 1994-től

Az LVDS-t 1994-ben vezették be ANSI/TIA/EIA-644 szabványként, és a differenciális jelátvitelt optimalizálja alacsony áramfelvétel és nagy adatsebesség szempontjából. A mindössze 350 mV-os kis differenciális feszültséglöket gyors kapcsolásokat tesz lehetővé minimális elektromágneses sugárzás mellett. Az LVDS ma széles körben elterjedt kijelző-interfészekben, soros adatkapcsolatokban és FPGA órajelezésben.

2.7 HCSL (High-Speed Current Steering Logic) – kb. 2002-től

A HCSL-t kifejezetten a PCI Express szabványhoz fejlesztették ki, és az első PCIe generáció óta a referencia-órajel szabvány. A PCI-SIG a HCSL-t árammód alapú differenciális jelként specifikálta, nagyon alacsony feszültséglökettel, a PCIe rendszerek 100 MHz-es referencia-órajeleihez optimalizálva. A HCSL ma nélkülözhetetlen minden PC-ben, szerverben és beágyazott rendszerben PCIe interfésszel.

3. Jelalak-áttekintés

Az alábbi diagramok a hét kimeneti típus idealizált jellefolyatásait mutatják. Figyelje meg a különböző feszültségtartományokat és jellöketeket – ezek meghatározók a következő vevőkkel való kompatibilitás szempontjából.

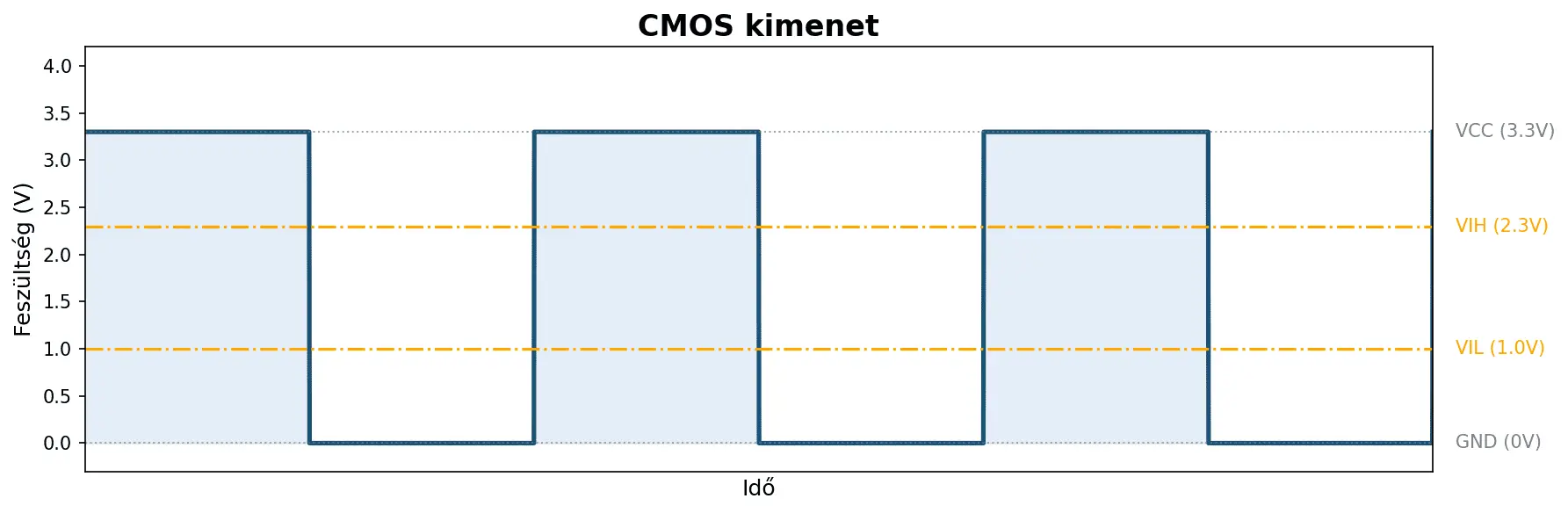

3.1 CMOS

Ábra 1: CMOS kimeneti jel – Rail-to-rail négyszögjel 0 V és VCC között (itt 3,3 V)

A CMOS jelet a GND és VCC közötti teljes feszültséglöket jellemzi. A bemeneti küszöbök VIL és VIH tipikusan a VCC 30 %-ánál ill. 70 %-ánál helyezkednek el, ami széles zajtűrést biztosít. A szimmetrikus kimeneti megható-struktúrák (P-csatornás/N-csatornás MOSFET) szinte azonos felfutási és lefutási időket tesznek lehetővé.

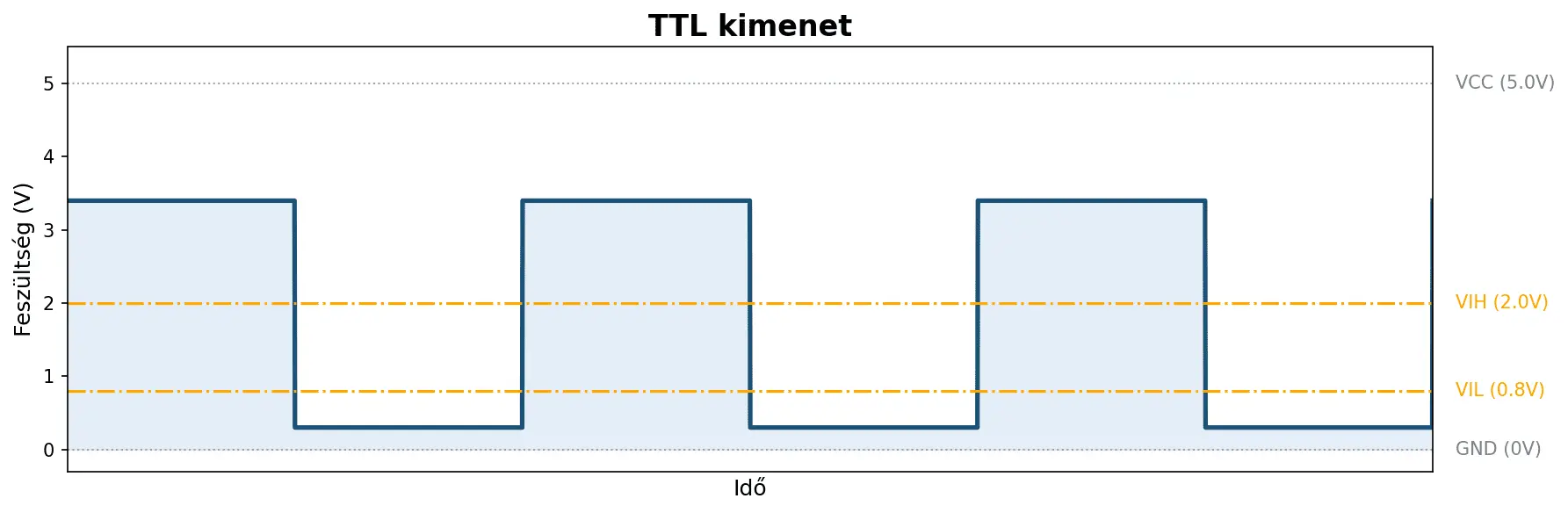

3.2 TTL

Ábra 2: TTL kimeneti jel – VOH tipikusan 3,4 V, VOL tipikusan 0,3 V 5 V táplálás mellett

A CMOS kimenettel ellentétben a TTL nem ér el rail-to-rail szinteket. A magas szint (VOH) tipikusan 3,4 V (minimum 2,4 V), az alacsony szint (VOL) legfeljebb 0,4 V. Az aszimmetrikus küszöbök (VIL = 0,8 V, VIH = 2,0 V) a bipoláris tranzisztor-architektúrából adódnak. Az ún. „tiltott zóna“ között 0,8 V és 2,0 V statikus üzemben nem foglalható el.

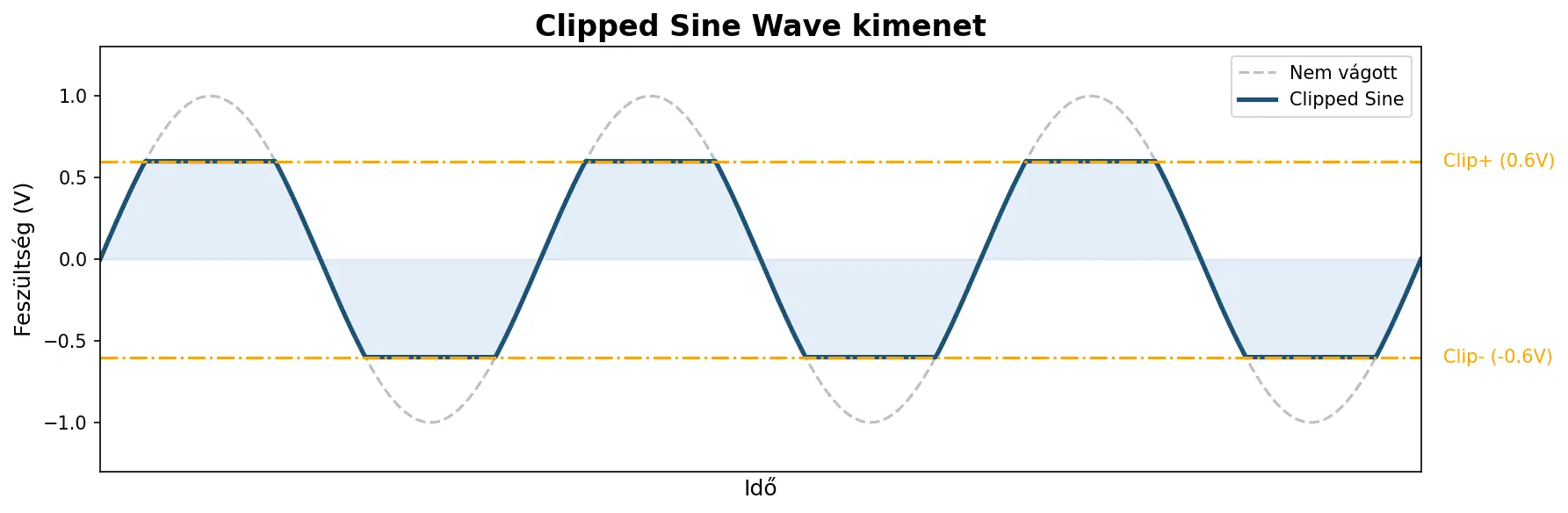

3.3 Clipped Sine Wave

Ábra 3: Clipped Sine Wave kimenet – Vágott amplitúdócsúcsokkal rendelkező szinuszjel

A Clipped Sine Wave kimenetenél a kvarcrezonátor természetes szinuszjelét meghatározott küszöbértékeknél levágják. A szaggatott vonal a vágatlan szinuszlefolytást mutatja. A clipping a tiszta szinusznál meredekebb nullapontit-átmeneteket hoz létre, ami megkönnyíti a következő logika vezérlését, miközben a felharmonikus tartalom mérsékelt marad.

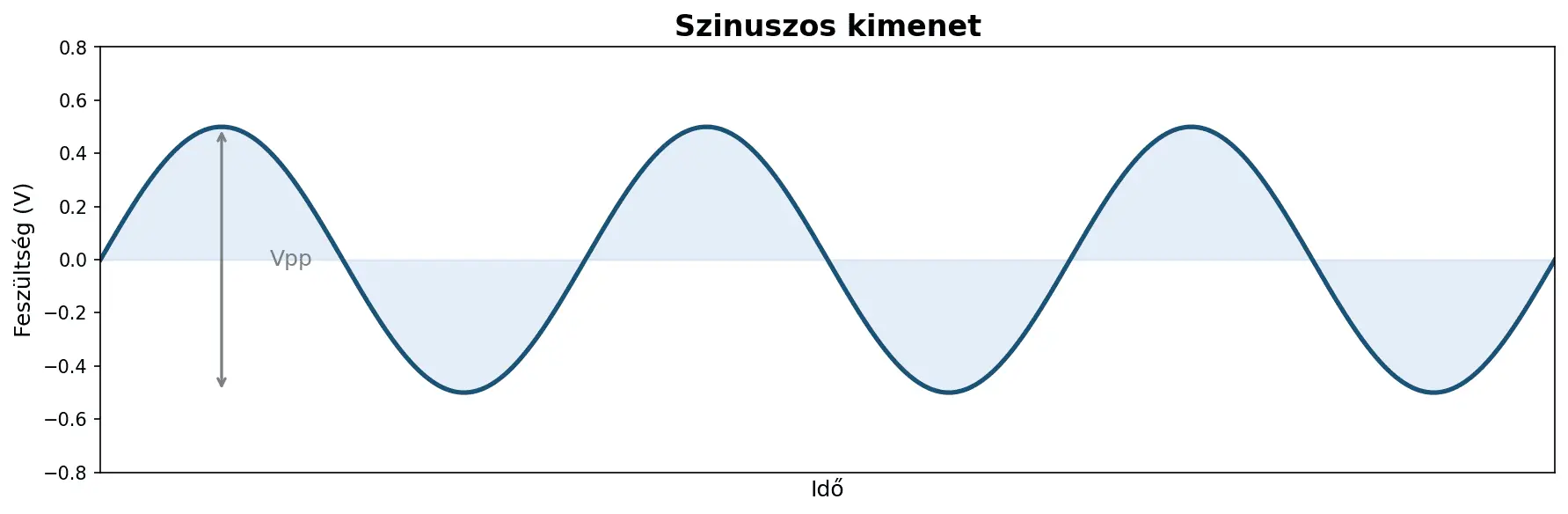

3.4 Sinus

Ábra 4: Szinuszos kimenet – Tiszta szinuszjel meghatározott csúcs-csúcs feszültséggel (Vpp)

A szinuszos kimenet az összes kimeneti forma közül a legtisztább spektrumot biztosítja: ideális esetben egyetlen spektrálvonalat az alapfrekvencián. Az amplitúdót csúcs-csúcs feszültségként (Vpp) vagy teljesítményként dBm-ben adják meg. Tipikus értékek 0,5-től 1,0 Vpp-ig vagy 0-tól +13 dBm-ig 50 Ω-os rendszerekben.

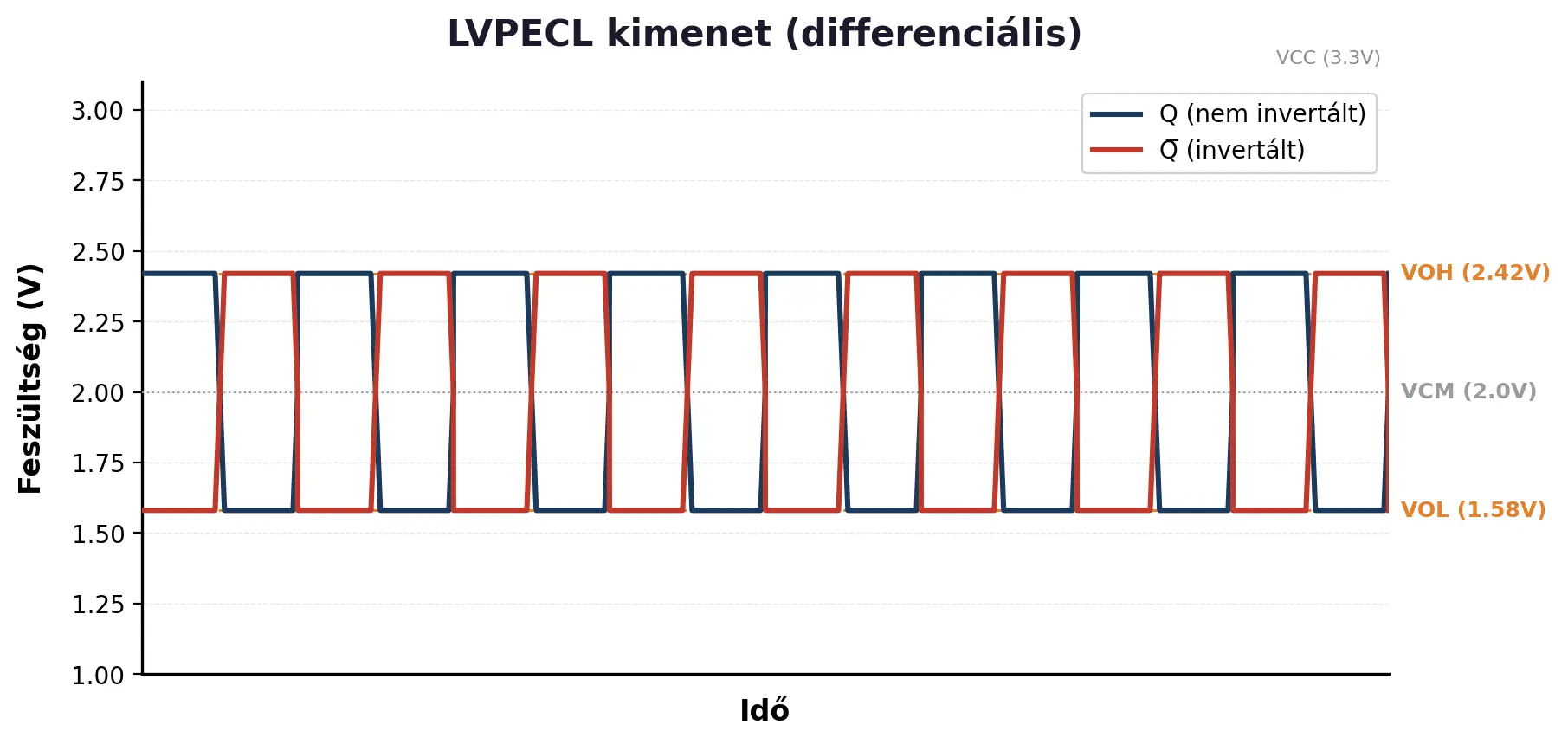

3.5 LVPECL

Ábra 5: LVPECL kimenet – Differenciális jel kb. 800 mV teljes lökettel VCC–1,3 V körül

Az LVPECL differenciális jelvezetést használ: két komplementáris kimenet (Q és Q̅) ellenfázisban kapcsol egy közös módú szint (VCM) körül, tipikusan VCC–1,3 V-nál. A differenciális feszültséglöket kb. 800 mV. Az áramforrás-architektúra extrém gyors kapcsolási időket tesz lehetővé minimális túllövési hajlammal.

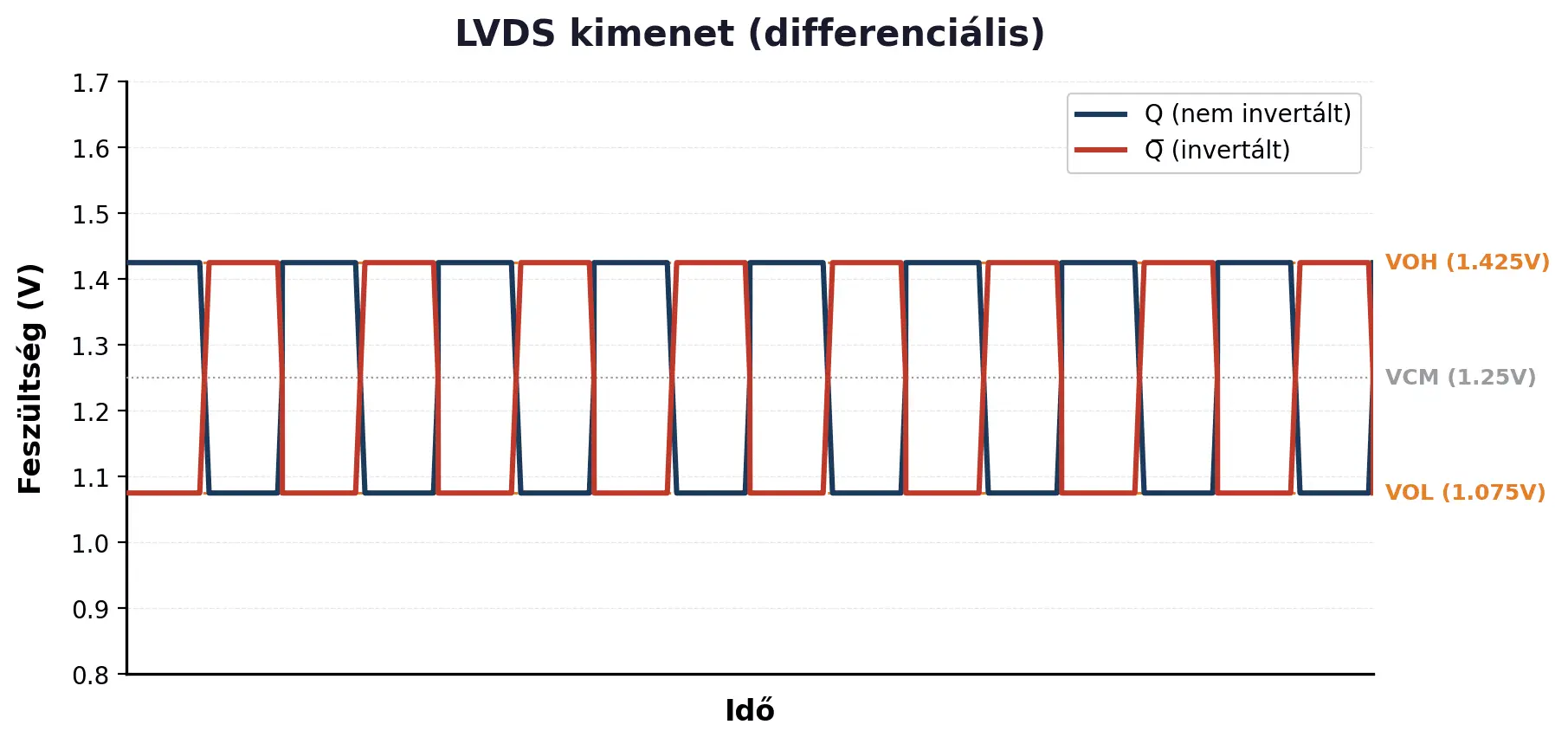

3.6 LVDS

Ábra 6: LVDS kimenet – Differenciális jel mindössze 350 mV lökettel 1,25 V közös módú szint körül

Az LVDS-t különösen alacsony, mindössze 350 mV-os differenciális feszültséglöket jellemzi. A közös módú szint 1,25 V-nál van. Az áramvezérelt meghatónak (tipikusan 3,5 mA) és a 100 Ω-os lezárásnak köszönhetően magas jelintegritás érhető el minimális áramfelvétel mellett. Az alacsony amplitúdó minimalizálja az elektromágneses sugárzást.

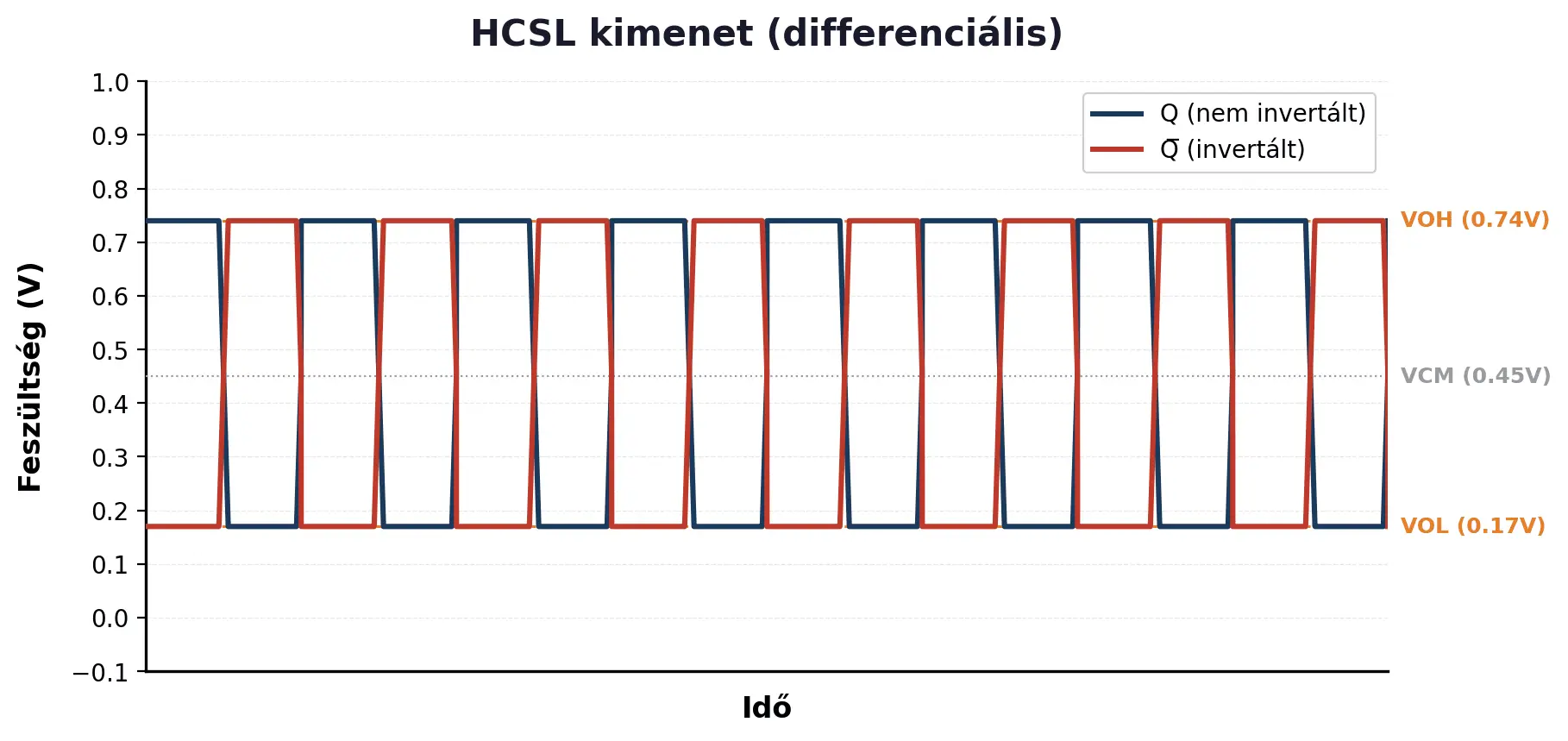

3.7 HCSL

Ábra 7: HCSL kimenet – Árammód alapú differenciális jel PCIe referencia-órajelekhez

A HCSL nagyon alacsony feszültséglökettel működik: a VOH tipikusan 0,74 V, a VOL 0,17 V, ami kb. 0,45 V-os közös módú szintet eredményez. Az áramvezérlési architektúra kifejezetten a PCIe specifikáció követelményeire optimalizált, és preciz impedancia-illesztést tesz lehetővé 50 Ω-os lezárásokon keresztül föld felé.

4. A kimeneti jelek összehasonlítása

Az alábbi táblázat összefoglalja mind a hét kimeneti típus legfontosabb tulajdonságait:

Typ | Jeltípus | VCC (V) | VOH/ VOL (V) | Diff. löket | Max. kb. frekv. | Tipikus alkalmazás |

| CMOS | Single-ended | 1,8-5,0 | VCC/ 0 | - | ~285 MHz | Mikrokontrollerek, FPGA-k, általános digitális technika |

| TTL | Single-ended | 1,8-5,0 | 3,4/ 0,3 | - | ~150 MHz | Legacy rendszerek, ipari vezérlések |

| Clipped Sine | Egyvégű | 1,8/2,5/3,3 | változó | - | ~200 MHz | Távközlés, RF alkalmazások |

| Sinus | Egyvégű | 3,3/5,0/12 | változó | - | >1 GHz | RF technika, mérőműszerek, frekvenciaszintézis |

| LVPECL | Differenciális | 2,5/3,3 | ~2,4/ ~1,6 | ~800 mV | >3 GHz | Hálózati berendezések, SONET/SDH, nagysebességű órajelezés |

| LVDS | Differenciális | 2,5/3,3 | ~1,43/ ~1,07 | 350 mV | >1 GHz | Kijelző-interfészek, soros kapcsolatok, FPGA órajelezés |

| HCSL | Differenciális | 3,3 | 0,74/ 0,17 | ~570 mV | ~200 MHz | PCI Express referencia-órajel (100 MHz) |

5. Lényeges különbségek részletesen

5.1 Single-Ended vs. differenciális

A kimeneti típusok közötti legalapvetőbb különbség a jelvezetés. A CMOS, TTL, Clipped Sine Wave és Sinus egyvégű (single-ended) jelek – közös földre referenciálnak. Az LVPECL, LVDS és HCSL ezzel szemben differenciális jelek két komplementáris vezetékkel. A differenciális jelek döntő előnyöket kínálnak magasabb frekvenciákon: elnyomják a közös módú zavarokat, kisebb feszültséglöketeket tesznek lehetővé, és ezáltal gyorsabb kapcsolási időket kevesebb elektromágneses sugárzás mellett.

5.2 Feszültséglöket és zajtűrés

A CMOS rail-to-rail kimenetével a legnagyobb abszolút feszültséglöketet és ezzel a legjobb statikus zajtűrést kínálja. A TTL az aszimmetrikus szintek miatt korlátozottabb zajtűréssel rendelkezik. A differenciális szabványok (LVPECL, LVDS, HCSL) kisebb feszültséglöketeiket a differenciális átvitel közös módú elnyomásával kompenzálják, így zajos környezetben gyakran megbízhatóbban működnek, mint az egyvégű jelek.

5.3 Áramfelvétel

A CMOS oszcillátorok statikus állapotban szinte nulla áramot fogyasztanak; a fogyasztás a frekvenciával arányosan nő (dinamikus teljesítményveszteség). A TTL a bipoláris architektúra miatt állandóan magasabb nyugalmi áramfelvétellel rendelkezik. Az LVPECL külső lezáró ellenállásokat igényel, és a differenciális szabványok közül a legmagasabb áramfelvétellel bír. Az LVDS alacsony áramfelvételéről ismert (tipikusan 3,5 mA meghatóáram). A HCSL áramfelvétel tekintetében az LVDS és az LVPECL között helyezkedik el.

5.4 Frekvenciatartomány és fő alkalmazási területek

Körülbelül 200 MHz-ig terjedő frekvenciákra a CMOS oszcillátorok a legtöbb esetben az elsődleges választásnak számítanak sokoldalúságuk, egyszerű áramköri kialakításuk és széles körű elérhetőségük miatt. Körülbelül 200 MHz felett differenciális kimenetek ajánlottak. Az LVPECL a legmagasabb frekvenciákat (>3 GHz) kínálja, és hálózati és telekommunikációs berendezésekben használják. Az LVDS széles középfrekvenciákat fed le, és különösen gyakori az FPGA és kijelző alkalmazásokban. A HCSL a saját résfelhasználási esetére van optimalizálva: a PCI Express 100 MHz-es referencia órajelére.

5.5 Lezárás és áramköri bonyolultság

A CMOS és TTL kimenetek rövid vezetékhosszak esetén általában nem igényelnek külső lezárást – ez különösen egyszerűvé teszi alkalmazásukat. Az LVPECL kötelezően külső lezáró ellenállásokat igényel (tipikusan: Thévenin lezárás VCC–2 V felé vagy ellenállások föld felé), ami növeli az áramköri bonyolultságot. Az LVDS-t alapértelmezésben 100 Ω-os differenciális ellenállással zárják le a vevőnél. A HCSL 50 Ω-os ellenállásokat használ föld felé minden kimeneten.

6. Túllövés az oszcillátor kimeneti jeleinél

6.1 Mi a túllövés?

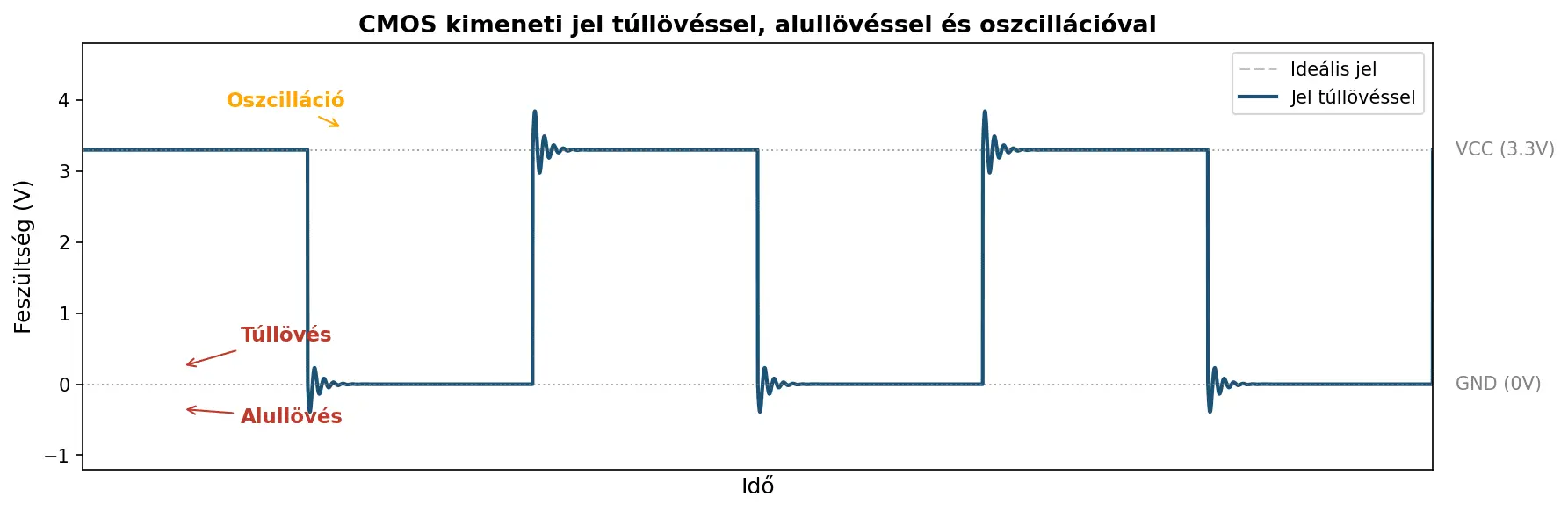

A túl- és alullendülések rövid feszültségcsúcsok, amelyek gyors kapcsolási műveletek során fordulnak elő. Felfutó élen a feszültség rövid ideig meghaladja a VCC-t (túllendülés), míg lefutó élen kissé a GND alá esik (alullendülés). Ezeket a csúcsokat gyakran csillapított rezgések követik, amelyeket "csengésnek" neveznek.

Az ok a kimeneti megható nagyon meredek kapcsolási éleinek és a vezeték, a tokozás és a terhelési kapacitás parazita induktivitásainak és kapacitásainak kombinációjában rejlik. Fizikailag rezgőkör jön létre a vezeték induktivitásából és a vevő bemeneti kapacitásából. Minél meredekebb a kapcsolási él és minél hosszabb a vezeték, annál kifejezettebb a túllövés.

Ábra 8: CMOS kimeneti jel túllövéssel – Túllövés VCC felett, alullövés GND alatt és azt követő ringing

6.2 Miért problémásak a túllövések?

A VCC fölé vagy GND alá menő túllövések a vevő-IC ESD védődiódáit nyitóirányba vezethetik, és így parazita áramokat generálhatnak. Legrosszabb esetben ez latch-up-hoz vezethet – kontrollálatlan áramfolyamhoz parazita tirisztor-struktúrákon keresztül a CMOS IC-ben, ami tönkreteheti az alkatrészt. Erős ringing továbbá többszörös kioldást okozhat az órajel-bemeneteken, ha a feszültség többször átlépi a kapcsolási küszöböt, ami hibás rendszerműködéshez vezet.

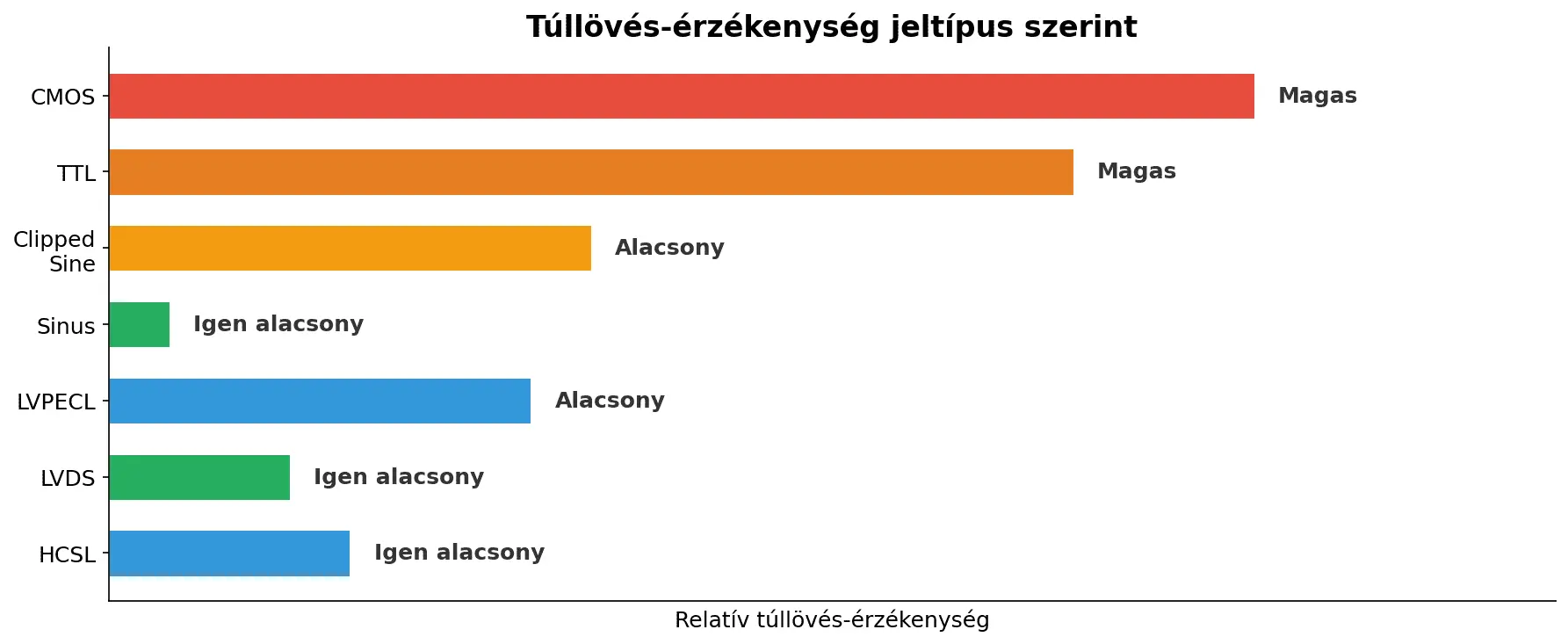

6.3 Összehasonlítás: túllövés jeltípus szerint

A túllövésre való hajlam jelentősen különbözik a különböző kimeneti típusok között. Az alábbi grafikon a relatív hajlamot mutatja összehasonlításban:

6.4 Túllövés egyvégű jeleknél

CMOS: A legerősebben érintett. A szimmetrikus P/N csatornás MOSFET meghatók nagyon meredek éleket generálnak, amelyek a vezeték-induktivitásokkal kombinálva kifejezett túllövést okoznak. Különösen modern alacsony feszültségű CMOS oszcillátoroknál (1,8 V) a túllövés a tápfeszültséghez képest jelentős lehet.

TTL: Szintén érzékeny, bár kissé más okokból. Az aszimmetrikus totem-pole kimeneti fokozat a felfutó élnél rövid áramcsúcsot generál, amikor mindkét tranzisztor egyidejűleg vezet (cross-conduction). A modern CMOS-hoz képest tipikusan kissé lassabb élek enyhén mérséklik a problémát.

Clipped Sine Wave: Lényegesen kevésbé érzékeny. A korlátozott amplitúdócsúcsok és a viszonylag lágy élek lényegesen kevesebb nagyfrekvenciás energiát termelnek, ami reflexiókat és ringing-et gerjeszthetne. A clipping természetes amplitúdó-korlátozóként hat, amely a túllövést már a jelben elnyomja.

Szinuszhullám: Gyakorlatilag immunis a klasszikus túllövésre. Mivel a jel nem tartalmaz hirtelen élátmeneteket, nem keletkezik szélessávú energiaimpulzus, amely gerjeszthetné a vonalrezonanciákat. Az impedancia-eltérések azonban állóhullámokhoz és visszaverődésekhez vezethetnek, amelyek bizonyos pontokon megváltoztatják a jel amplitúdóját. Ezt klasszikus RF lezárással (50Ω vagy 75Ω lezárás) szabályozzák.

6.5 Túllövés differenciális jeleknél

LVPECL: Az áramforrás kimeneti fokozatnak köszönhetően belsőleg jól elnyomott. Az áramvezérlés természetes módon korlátozza a maximális élmeredekséget. Elégtelen lezárás esetén mégis előfordulhatnak reflexiók, mivel az LVPECL nagyon magas frekvenciákon működik. A helyes Thévenin vagy emitterkövető kapcsolás itt döntő – nem elsősorban a túllövés miatt, hanem a helyes munkapont biztosításához és a reflexiók elkerüléséhez.

LVDS: Konstrukcióból adódóan nagyon robusztus. Az áramvezérelt megható tipikusan 3,5 mA állandó áramot szállít a 100 Ω-os differenciális lezárásba, ami fizikailag korlátozza a feszültséglöketet. Még impedancia-szakadások esetén is kicsik maradnak a reflexiók, mivel a mindössze 350 mV-os alacsony feszültséglöket kevés energiát biztosít zavarokhoz. Az LVDS az egyik legelnézőbb szabvány a jelintegritás tekintetében.

HCSL: Az áramalapú architektúrának köszönhetően hasonlóan viselkedik, mint az LVDS. A nagyon alacsony feszültséglöket és az 50 Ω-os lezárás föld felé tiszta impedancia-illesztést biztosít. A PCIe specifikációban a megengedett túllövések kifejezetten definiáltak és szorosan toleráltak, így a HCSL-megfelelő oszcillátorok eleve teljesítik ezeket a követelményeket.

6.6 Ellenintézkedések a túllövés szabályozására

Az egyvégű jeleknél (különösen CMOS és TTL) a leghatékonyabb intézkedés egy soros ellenállás közvetlenül az oszcillátor kimenetén, tipikusan 22 és 47 Ω közötti tartományban. Ez az ellenállás a vezetékimpedanciával együtt feszültségosztót képez, amely csillapitja az élet és elnyeli a reflexiókat. Az optimális érték a vezetékimpedancia és a megható kimeneti impedanciája közötti különbségből adódik.

Emellett segítenek a rövid, impedancia-kontrollált vezetékek, az átvezetések (via-k) minimalizálása az órajel-vezetéken, a folyamatos földsík a jelvezetk alatt, valamint elegendő leszúrő kondenzátor az oszcillátor közelében (tipikusan 100 nF kerámia plusz 10 µF). Egyes CMOS oszcillátor-gyártók emellett kontrollált élmeredekségű (Slew Rate Control) modelleket is kínálnak, amelyek már a meghatóban enyhítik a problémát.

Differenciális jeleknél (LVPECL, LVDS, HCSL) a helyes, specifikáció-megfelelő lezárás a legfontosabb intézkedés. Emellett a differenciális pár két vezetékét mindig azonos hosszúsággal és szoros csatolással kell vezetni, hogy minimalizálják a skew-t (futtatási időkülönbségeket) és fenntartsák a közös módú elnyomást.

7. Döntési segédlet

A megfelelő kimeneti típus választása lényegében négy tényezőtől függ: az igényelt órajel-frekvenciától, a vevő logikai családjától, a rendelkezésre álló teljesítménybudétól és a jelintegritással szemben támasztott követelményektől.

Alkalmazási eset | Ajánlás |

| Általános digitális technika, µC, FPGA-I/O (~200 MHz-ig) | CMOS – A legegyszerűbb és leggazdaságosabb megoldás, rail-to-rail, a legszélesebb elérhetőség, rugalmas tápfeszültség (1,8–5,0 V) |

| Legacy 5V rendszerek, ipari vezérlések | TTL – Közvetlenül kompatibilis régebbi 5V logikai családokkal; egyre inkább CMOS váltja fel 5V táplálással |

| RF alkalmazások, transzformátor alapú áramkörök | Clipped Sine Wave vagy Sinus – Az alacsonyabb felharmonikus tartalom csökkenti az EMC problémákat és preciz frekvenciaszintézist tesz lehetővé |

| Nagysebességű hálózati berendezések (>622MHz) | LVPECL – Legmagasabb kapcsolási sebesség, ideális SONET/SDH, Ethernet PHY és backplane órajelekhez |

| FPGA órajelezés, soros adatátvitel, kijelző-interfészek | LVDS – Optimális kompromisszum sebesség, áramfelvétel és EMC viselkedés között |

| PCI Express referencia-órajel | HCSL – A PCI-SIG által PCIe rendszerekhez specifikált egyetlen órajel-szabvány |